# **Electrodeposited Mn-Co Alloy Coating For SOFC Interconnects**

H.A. McCrabb<sup>1</sup>, Savidra Lucatero<sup>1</sup>, T.D. Hall<sup>1</sup>, H. Zhang<sup>2</sup>, X. Liu<sup>2</sup>, S. Snyder<sup>1</sup>, and E.J. Taylor<sup>1</sup>

<sup>1</sup>Faraday Technology Inc., 315 Huls Dr., Clayton, OH 45315, USA

<sup>2</sup>West Virginia University, Dept. of Mechanical and Aerospace Eng. ESB, Morgantown, WV, 26506, USA

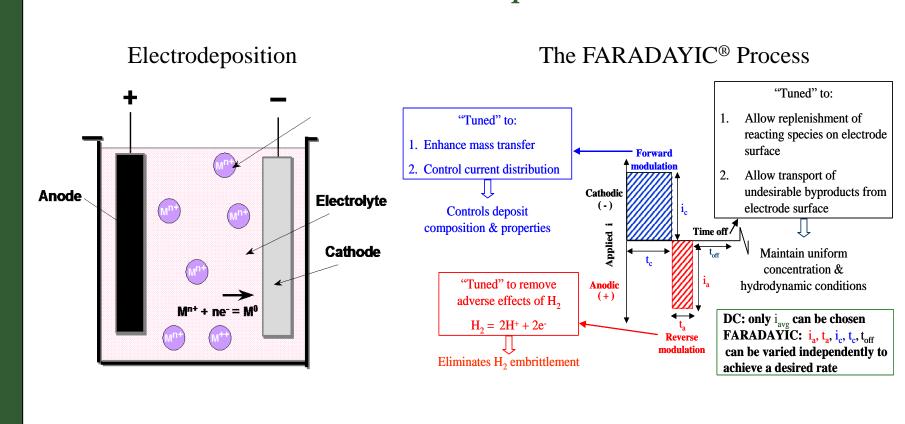

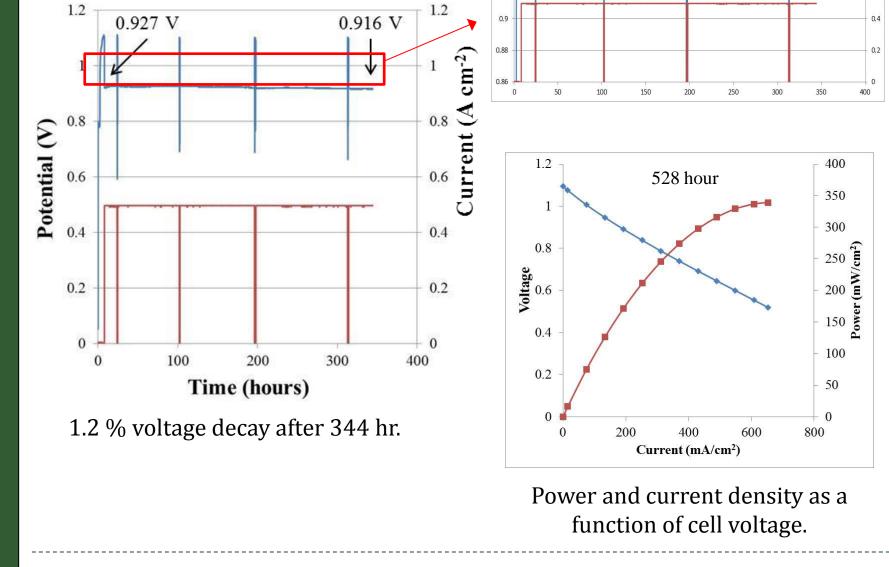

#### **Overall Objective Technical Results Previous Accomplishments** Long-term On-cell Performance Evaluation Varying Cobalt Concentration Develop, optimize & validate an inexpensive manufacturing 20:1 Co:Mn 5:1 Co:Mn process for coating metallic SOFC interconnects with Co and Mn. **Button Cell Dimensions** Cell Test Fixture Introduction ← 3/4in.→ Reducing SOFC operating temperatures below 1000 °C has permitted less resistive and expensive ferritic stainless steel interconnects to manning replace ceramic materials. However, even specially developed ferritic MICA Gaske alloys operated at elevated temperatures for lengthy periods of time $(Co, Mn)_3O_4$ coated form a chromia scale that increases the interconnect resistance and **Tube Flang** 441 stainless steel button cell Pt Mesh results in chrome diffusion from the interconnect to the cathode that **Contact Paste** causes a reduction in cathode performance. One attractive method to Minor Cr diffusion Minor Cr diffusion resolve the chromia scale growth and diffusion issues is to Current Lead electrodeposit a Mn-Co alloy coating onto the interconnect surface **2000 Hour Thermal Soak** and subsequently convert it to a $(Mn,Co)_3O_4$ spinel. Top: coated Under funding from the Department of Energy, Faraday Technology and WVU are developing, optimizing and validating an *Constant Current Performance* (0.5 A cm<sup>-2</sup>) electrodeposition process to apply Mn-Co alloy coatings to SOFC

interconnects. The FARADAYIC<sup>®</sup> Electrodeposition Process is used to deposit a Mn-Co alloy that is subsequently oxidized to a spinel by thermal exposure at high temperatures in an oxidizing environment. Coatings exposed to extended thermal soaks exhibited relatively dense, crystalline microstructures that prevented chrome diffusion through the coating and maintained low area specific resistance. Faraday has scaled its process capabilities to industrial size SOFC interconnects with gas flow features.

# Approach

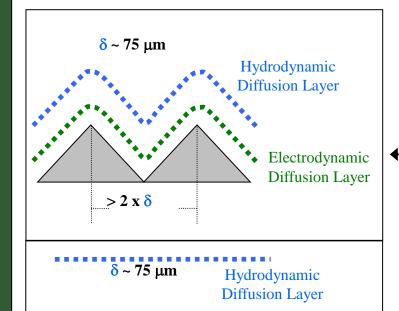

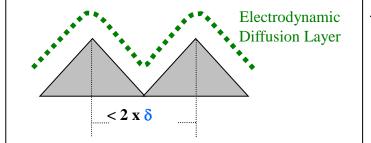

The appropriate waveform can alter the thickness of the pulsating diffusion layer and effectively focus or defocus the current distribution to create non-uniform or uniform deposition respectively.

← Macroprofile: Diffusion layer tends to follow the surface contour. Mass transport control results in a uniform current distribution or a conformal deposit during deposition.

1.2 -

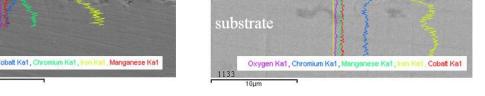

Left) Mn-Co alloy coating, Right) After exposure to a 95% H<sub>2</sub>/5%N<sub>2</sub> atmosphere for two hours at 800 °C with a 4 °C min<sup>-1</sup> ramping & cooling rate & a 50%  $H_2/50\%N_2$  ramping & cooling atmosphere

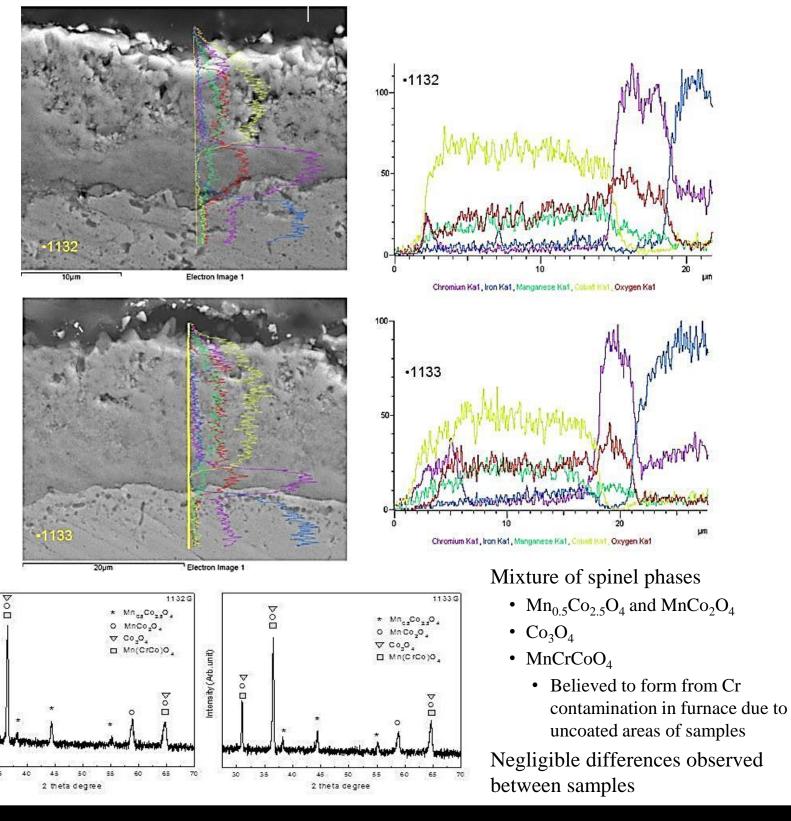

| Sample No. | 2 hour thermal soak<br>pre-treatment | Mn-Co coating<br>thickness (μm) | Chromia scale<br>thickness (µm) | ASR (mΩ cm <sup>2</sup> ) |

|------------|--------------------------------------|---------------------------------|---------------------------------|---------------------------|

| 1132H      | H <sub>2</sub>                       | 12                              | 5                               | 27.6                      |

| 1133H      | Air                                  | 17                              | 4                               | 29.1                      |

| 1135H      | Air                                  | 14                              | 5                               | 30.6                      |

| 1136H      | H <sub>2</sub>                       | 16                              | 6                               | 21.6                      |

| 1137H      | Air                                  | 15                              | 5                               | 26.0                      |

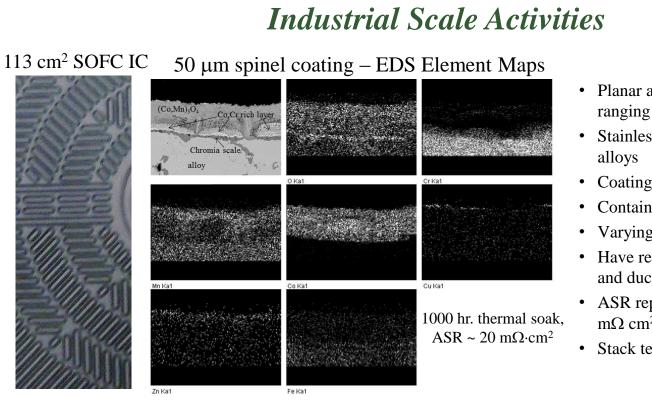

Planar and patterned interconnects ranging from  $100 - 225 \text{ cm}^2$ Stainless steel alloy & proprietary Coatings from a few microns to 50 µm Contained proprietary flow fields • Varying ratios of Co:Mn Have received reports of good adhesion and ductility for the oxide coatings • ASR reported in the range of 10 - 20 $m\Omega \ cm^2$ • Stack testing next

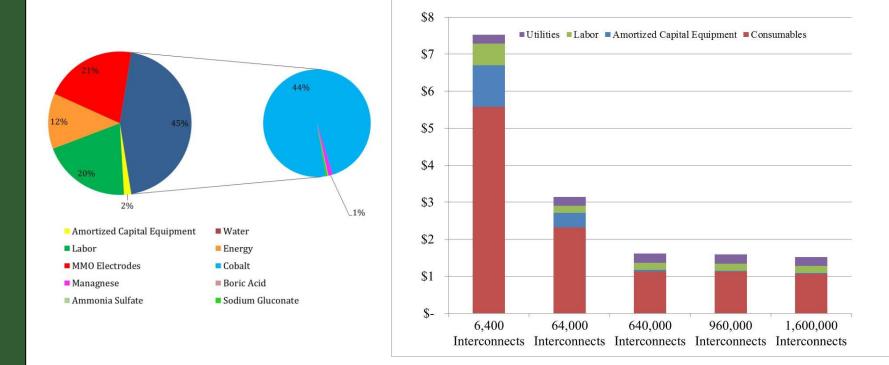

# **Economic Analysis**

Current cost analysis of coating process based upon batch manufacturing of 1,600,000 plates per annum at a cost of ~\$0.98 per 625 cm<sup>2</sup> coated interconnect.

10 µm thick cathode coating\*

### The FARADAYIC® Electrodeposition Process

← Microprofile: Diffusion layer thickness surface roughness. Mass transport control results in a non-uniform current distribution.

### The FARADAYIC<sup>®</sup> Electrodeposition process...

- Enables alloy composition control

- Enables control of coating uniformity for flow field patterns

- Maintains fast processing times to enable high throughput manufacturing

- Is an inexpensive manufacturing process for SOFC interconnect coatings

|                | Milestones                                                   |                       |                     |  |  |

|----------------|--------------------------------------------------------------|-----------------------|---------------------|--|--|

| Fiscal<br>Year | Title                                                        | Planned<br>Completion | Percent<br>Complete |  |  |

| 2011           | 1. Design/modification of 10" x 10" electrodeposition cell   | May 2011              | 100%                |  |  |

| 2012           | 2. Long-term high temperature, thermal evaluation            | September 2012        | 100%                |  |  |

| 2012           | 3. Process development for 4"x4" planar interconnects        | May 2012              | 100%                |  |  |

| 2013           | 4. Process development for 4"x4" pattern interconnects       | June 2013             | 100%                |  |  |

| 2013           | 5. Long-term on-cell performance evaluation                  | August 2013           | 100%                |  |  |

| 2013           | 6. Qualification/demonstration of IC in single cell test rig | September 2013        | 50%                 |  |  |

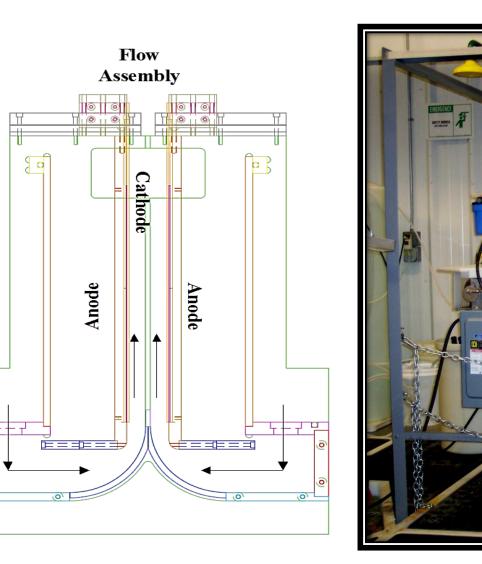

# **Processing Equipment**

#### **Electrochemical Cell**

Based upon Faraday's electrochemical cell design that facilitates uniform flow across the surface of a flat substrate (US patent #7,553,401; 7,947,161; 8,226,804)

ACID

## **FARADAYIC®** Electrodeposition Cell Features:

Cathode side only or cathode and anode side coatings Interconnect coatings of various shapes and size ranging from  $6.5 \text{ cm}^2 - 645 \text{ cm}^2$

#### Cost is ~\$1.72/IC for cathode and anode side coating

# **Accomplishments/Future Work**

#### FY 2013 Accomplishments

- Completed long-term on-cell performance evaluation of button cells

- Updated economic cost evaluation

- Delivered coated interconnects to commercial partners for performance evaluation via SOFC stack testing

# **Future Work**

Qualification/demonstration of interconnect coating in single cell test rig under ideal SOFC operating conditions by potential commercial partners

# Acknowledgements

This material is based upon work supported by the Department of Energy under Grant No. DE-SC0001023 . Any opinions, findings, and conclusions or recommendations expressed in this material are those of the authors and do not necessarily reflect the views of the DOE.

#### Principal Investigator: Heather McCrabb, Company Name: Faraday Technology, Inc., Address: 315 Huls Drive, Clayton, OH 45315, Phone: 937-836-7749, E-mail: heathermccrabb@faradaytechnology.com, Company website: faradaytechnology.com